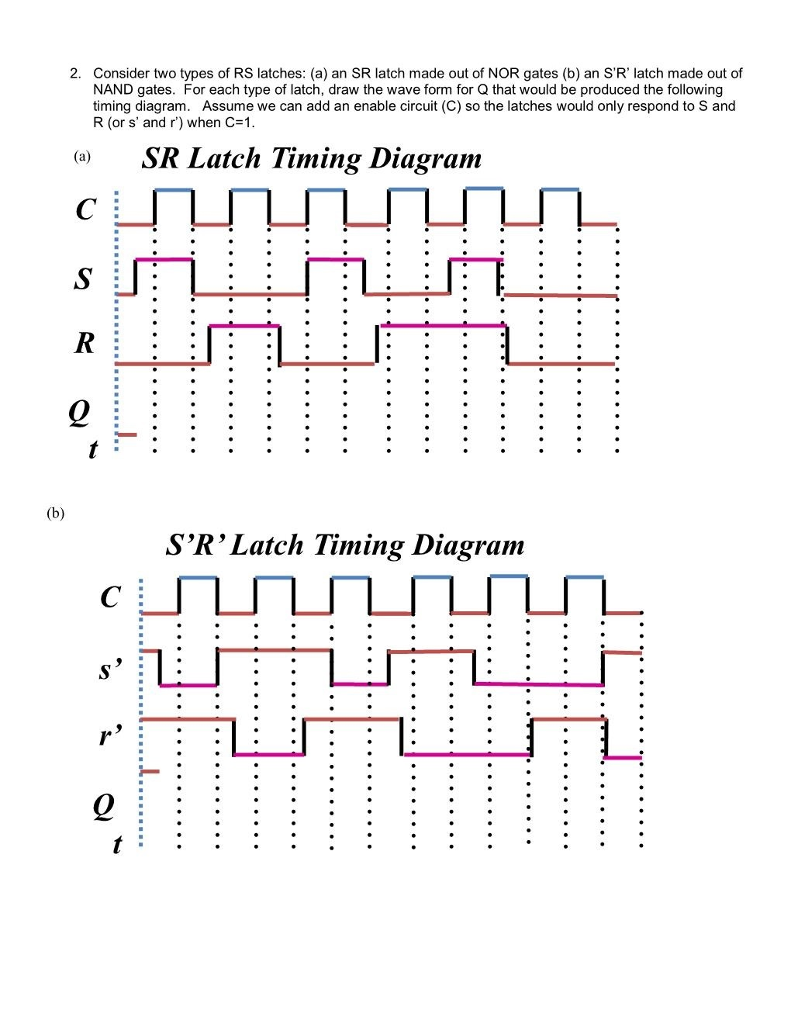

35 d latch timing diagram

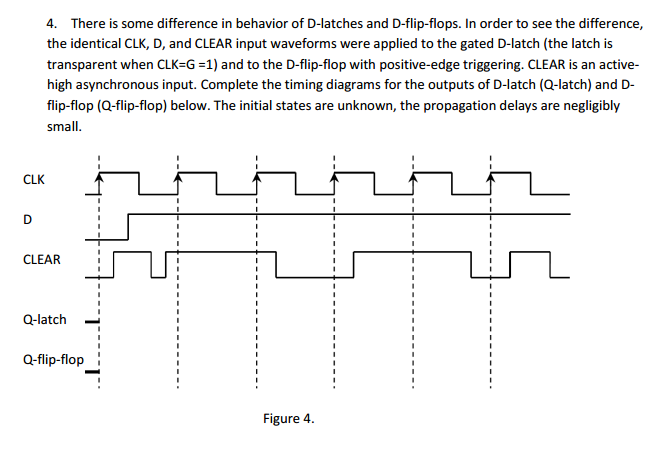

Indicate in the provided timing diagram the behavior of the output of the flip-flop and the latch (q_mick and q_keith) as well as the behavior of the output bus Timing diagram to complete: Answer ( which I do NOT understand, the answer itself and don't even get me started on the handwritting! haha) Questions about the timing diagram on the right: G looks like a ramp shape that goes down. Does that mean voltage was a higher constant then went down I've been googling d latch timing diagrams to figure out the above- haven't found it yet but did notice that alot of other d latch timing diagrams look...

*I started thinking about how to make a world where having a game system and summoning heroes to fight an Evil Lord would not just be possible, but totally logical. In the end, I came up with this. I'm very proud of it.* # A History of Kishar and Its Magic Back when the gods were around, mortals first started using magic through being blessed by a god or by virtue of being descended from them. Such people had innate magic powers. The Authority to do something. An intent so powerful that struct...

D latch timing diagram

ECE 443. D Latch D latch is a level sensitive memory element, while the D ip-op (FF) is an edge. Timing Analysis The setup time constraint indicates that state_next MUST be stabilized at least Tsetup before the next sampling edge at t5 -- given by t4 in the timing diagram t3 < t4. This is an adventure for a level 7 party of adventurers. Note this adventure uses multiple statblocks from *Volo’s Guide to Monsters*, as well as items from *Xanathar’s Guide to Everything*. **Premise:** centuries ago, a group of Orcus cultists conspired with several druids to combine their respective disciplines and bring forth new monstrosities. Their plans progressed as far as successfully capturing and slaying a dragon for their masterpiece ritual, but this also caused them to be discovere... I'm not a psychologist, but I find this stuff interesting, so here's some stuff about how people can get drawn into conspiracies: - First there's a really cool bias I don't see people talk about; people with a conspiracy bias tend to like detailed stories, or more specifically they have a ["conjunction bias"](https://core.ac.uk/download/pdf/42383586.pdf). If you ask someone what is more likely, that someone robbed a bank, and that they robbed a bank with a loaded gun they threatened everyone ...

D latch timing diagram. *Well, it has been a while. I suppose I';d better number these, so this is number 3. I was thinking, if I wanted to showcase some human tech to the aliens in my little universe, what would I show them?* --- The little crystalline crablike thing skittered across the non-slip surface of the beverage dispensing station. Hot water, fenal leaf, times two, one with sucrose syrup, one without, its six legs deftly manoeuvring around the equipment, its four pincer arms measuring, stirring. The lizardli... Digital Circuits - Latches, There are two types of memory elements based on the type of triggering that is suitable to operate it. Latches operate with enable signal, which is level sensitive. Whereas, flip-flops are edge sensitive. We will discuss about flip-flops in next chapter. S r latch timing diagram is important information accompanied by photo and HD pictures sourced from all websites in the world. Download th... A door is locked, but a normal key won't work to open it. What odd item, or combination of items, does the party need to find to open the door? 1. A Warforged hand to put in the hand scanner device next to the door, but a dead hand won't work. They need to find a power source to keep the hand active to interface with the scanner. 2. A rare jade orchid. There's a nose on the door and the party heard the person who made the dungeon loves the scent of jade orchids. 3. A lot of water. The door will...

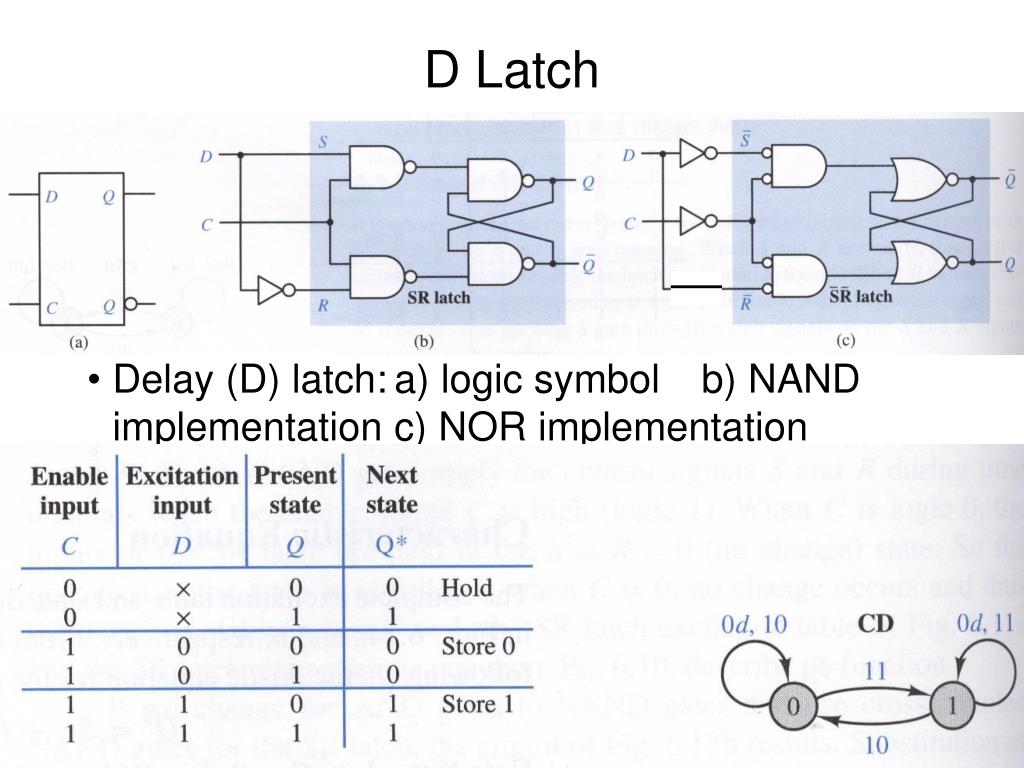

For timing requirements, level sensitive latches are widely used in high performance ICs where timing analysis is more critical and challenging [9-1 1]. In the approaches presented in the literature, the latch delay model Figure 1. Timing diagram of latch. The situation with the latch is different from flip-flop. State Transition Diagram: The excitation table in graphical form. 3-7. S R. Latch. • Similar - made from NANDs. 3-8. Clock - Periodic event, causes state of memory element to change Setup time - time that D must be available before clock edge Hold time - time that D must be stable after clock edge. •latches -sr latch -nor gates -sr latch w/ control -d latch. • Timing diagrams allow you to see how a sequential system changes with time using different inputs. • For instance, a timing diagram for a D latch might look like the following. I'm trying to interface a Parallel LVDS ADC to a Nexys Video, through the FMC interface. [Diagram](https://preview.redd.it/nez9mcdeimw71.png?width=6600&format=png&auto=webp&s=948bea2d1b18d90f1f0991c6c197f9f4e4a75a64) However, I'm not getting anything understandable in the digital input.I don't know if I'm doing the timing properly. I placed some input delays and PLL's trying to fix this, but timing is a mess. &#x200B; [Timing Results](https://preview.redd.it/huy8ynv9mmw71.png...

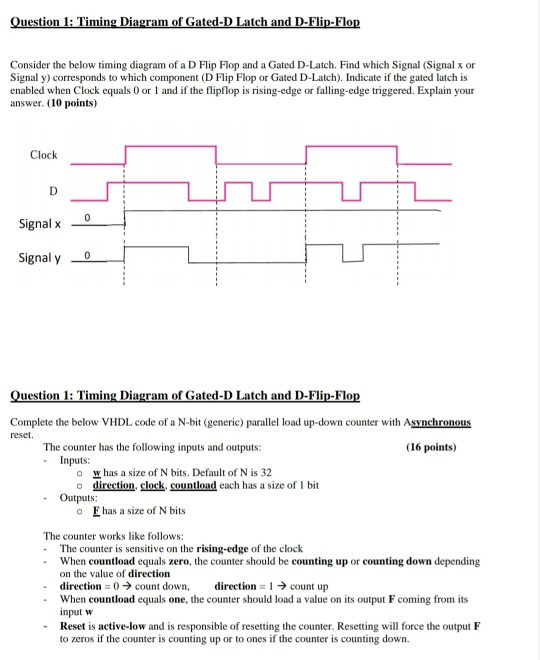

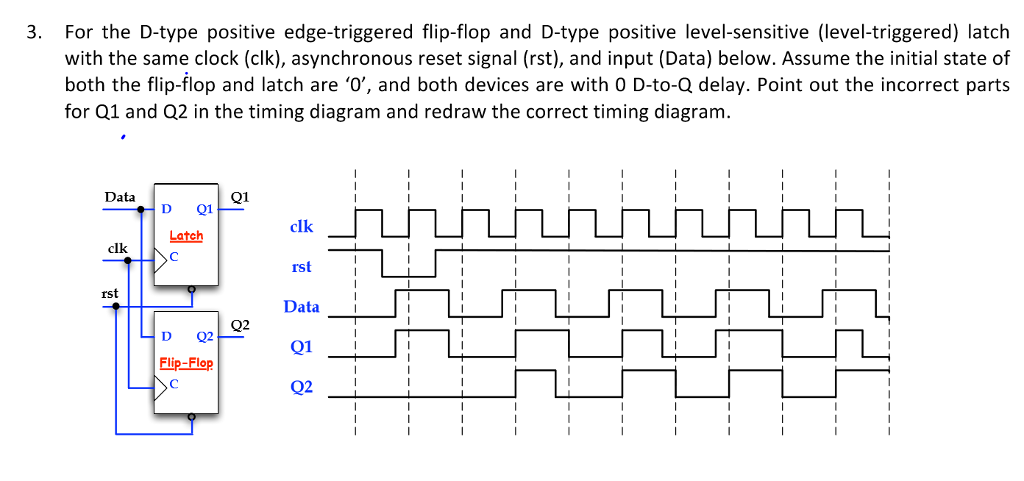

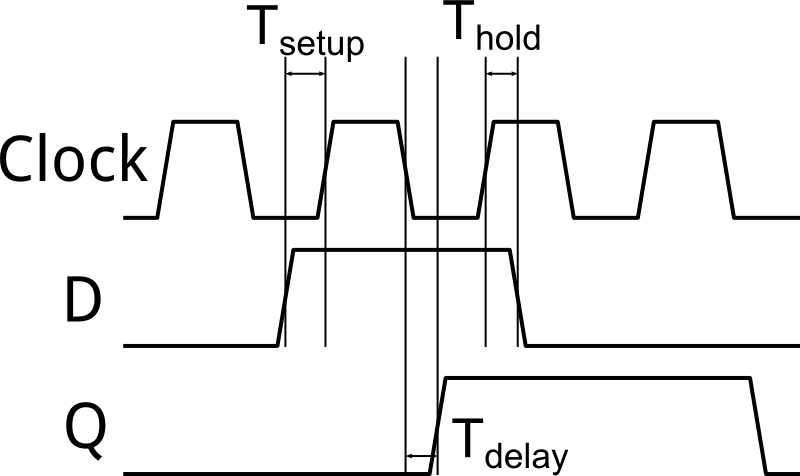

(Truth Table & Timing Diagram). December 20, 2020February 24, 2012 by Electrical4U. Contents. What is a D Flip Flop (D Latch)? A D Flip Flop (also known as a D Latch or a 'data' or 'delay' flip-flop) is a type of flip flop that tracks the input, making transitions with match those of the input D. The... D-latch time diagram with preset and clear? Ask Question. I'm trying to study for an exam and I've been searching for any videos or images or pages explaining the time diagram for the D-Latch that involves the preset and clear. The given timing diagram shows one positive type of edge triggered d flip flop; there is clock pulse CLK, D the input to the D flip flop, Q the output of the D flip flop; as you can see, the changes in output are happening during the transition of the clock pulse from low to high, because it is a timing diagram of a positive edged D type flip flop. [Retaliation (6)](https://www.reddit.com/r/HFY/comments/q8rl4d/retaliation_6/) “Hey! Watch it!” A rough shove sent him stumbling forwards, the rations skidding out from the cradle in his arms and clanking noisily against the metal floors. “Keep your eyes ahead of you, kid, we’re not here to play games,” the gruff voice spat at him from above as Trevor knelt to pick up the fallen goods. He reigned in the curses that were teetering on his tongue, opting to let the other man proceed on his way w...

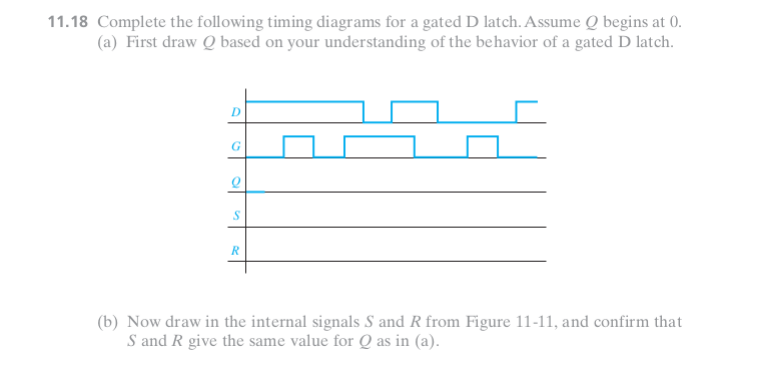

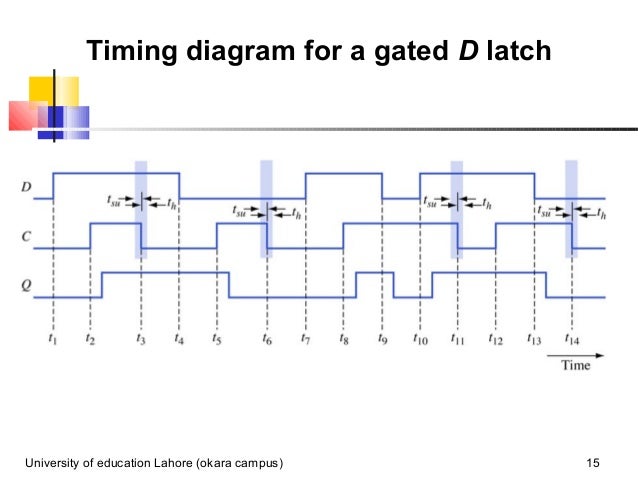

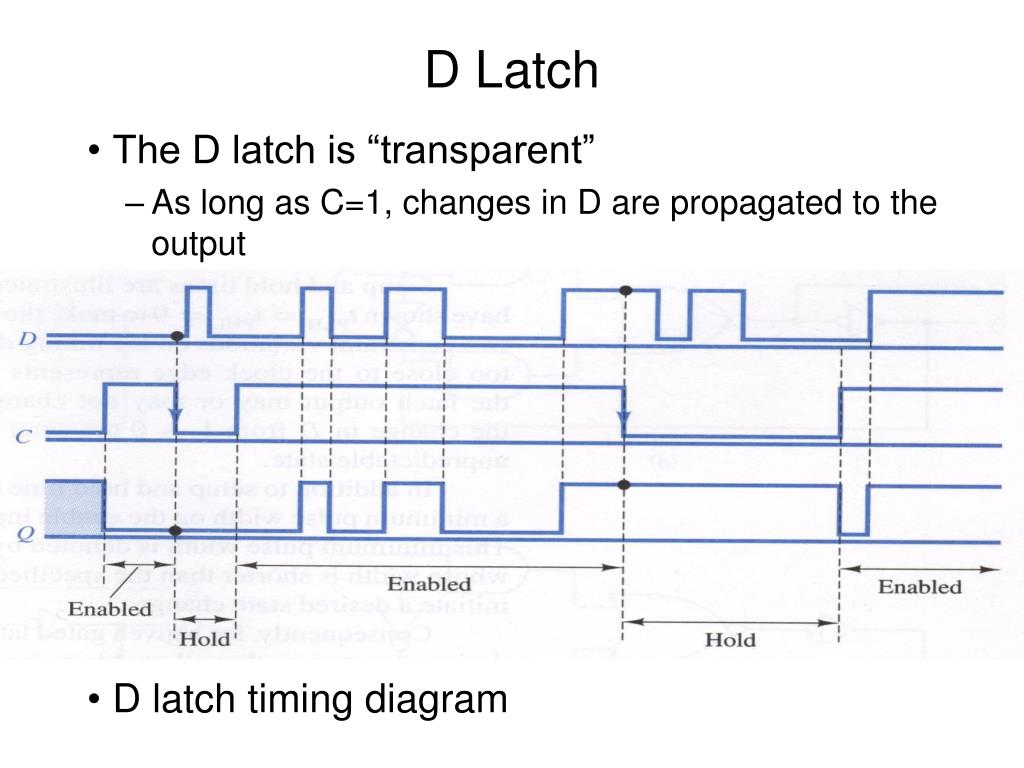

A timing diagram for the D-latch is shown below in Fig. 7. Note that when the Gate input is asserted, the output Q simply "follows" the input. Figure 7. D-latch timing diagram. D Flip-Flop. All useful memory devices have at least two inputs—one for the Data signal to be memorized, and a timing...

If the above diagram is confusing at all, the next diagram should make the concept simpler: Like both the S-R and gated S-R latches, the D The D latch is nothing more than a gated S-R latch with an inverter added to make R the complement (inverse) of S. Let's explore the ladder logic equivalent of a...

The following circuit and timing diagrams illustrate the differences between D-latch, rising edge triggered D flip-flop and falling 2-3-3. Develop a testbench to test and analyze the design behavior. It should generate the input stimuli as shown in the timing diagram. 2-3-4. Add the appropriate board...

Positive Static Latch Timing Diagram. • Other latch types: - JK latch: Removes "not allowed" state - e.g., toggles when inputs are both 1 - T latch: Toggles when T input = 1 - D latch: Output = D input.

The Gated D Latch Timing Diagram. February 6, 2012 ECE 152A - Digital Design Principles 28 The Edge Triggered D Flip-Flop

**PART FIVE HUNDRED AND SIXTY-ONE** [\[Previous Chapter\]](https://www.reddit.com/r/redditserials/comments/qqthg1/bob_the_hobo_a_celestial_wars_spinoff_part_0560/) [\[](https://www.reddit.com/r/redditserials/comments/ofifuj/bob_the_hobo_a_celestial_wars_spinoff_part_0451/)[NEXT CHAPTER](https://www.reddit.com/r/redditserials/comments/qtozez/bob_the_hobo_a_celestial_wars_spinoff_part_0562/)[\]](https://www.reddit.com/r/redditserials/comments/orb488/bob_the_hobo_a_celestial_wars_spinoff_part_0469...

Let's compare timing diagrams for a normal D latch versus one that is edge-triggered In the second timing diagram, we note a distinctly different response in the circuit output(s): it only responds to the D input during that brief moment of time when the enable signal changes, or transitions, from low to high.

**PART THREE HUNDRED AND SEVENTY-EIGHT** ***((For those who would like to start from the beginning, Part One can be found*** [***HERE***](https://www.reddit.com/r/redditserials/comments/fs6i9s/bob_the_hobo_a_celestial_wars_spinoff_part_0001/?utm_source=share&utm_medium=web2x) ***))*** ***Tuesday*** “So, what’s your take on Donna Bertram?” Cromwell asked as she and Lucas left the yoga studio. “She definitely has something to hide,” Lucas said, keeping his voice low despite the busyness of...

##Big dungeon crawl with gritty and cruel rules. I'm planning on running a massive dungeon crawl for some friends and I want to get some ideas for rooms that they might encounter. The more grim and gruesome the better. 1. A study for teaching/learning 2. A garden to grow all of the alchemy and poisonous plants a wizard would ever need 3. A power source of some kind to generate magical power. 4. A workshop/smithy to make parts and weapons for his mechs 5. An interrogation room to get all the ju...

How to draw timing diagram for D Latch and D Flip-flop? Timing diagram for D flop are explained in this video, if you have any questions please feel free to comment below, I will respond ...

Things have been busy so, I apologize for the delay. I know lots of you love these stories. *Last Friday night...Yeah, I think we broke the law...Always say we're gonna stop, whoa* Friday, or in the alternative: What part of call me was not clear? I get to my desk at the usual time and deal with the usual bullshit. I got a SCAR 16s here on consignment because a customer of mine bought them from dealers that were less than reputable and lied about the condition of/country of origin of their m...

Flip-flop timing. n Setup time tsu: Amount of time the input must be stable before the clock transitions high (or low for negative-edge triggered FF). Class example: Draw the timing diagram. CSE370, Lecture 14. 10. How do we make a latch? u Two inverters hold a bit. n As long as power is applied.

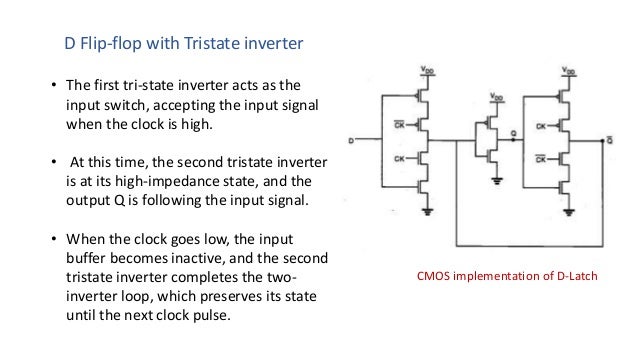

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information – a bistable multivibrator.The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic.Flip-flops and latches are fundamental building blocks of digital ...

Figure 1 – A Ladder Logic Latch. The operation of the ladder logic in Figure 1 is illustrated with a timing diagram in Figure 2.. A timing diagram shows values of inputs and outputs over time. For example the value of input A starts low (false) and becomes high (true) for a short while, and then goes low again.

A sample timing diagram for the operation of the D latch with enable is shown in Figure 9(d). Between t0 and t1, the latch is enabled with E = 1 so the output Q follows the input D. Between t1 and t2, the latch is disabled, so Q remains stable even when D changes. 7.6 D Flip-Flop.

Questions about the timing diagram on the right: G looks like a ramp shape that goes down. Does that mean voltage was a higher constant then went down I've been googling d latch timing diagrams to figure out the above- haven't found it yet but did notice that alot of other d latch timing diagrams look...

D latch can be active high input or active low input latch. D flip-flop in which data input is always active high, where set or reset input can be active high or active low input. D latch is always a level triggered circuit. D flip-flop can be level triggered or edge triggered circuit. Less number of transistor is …

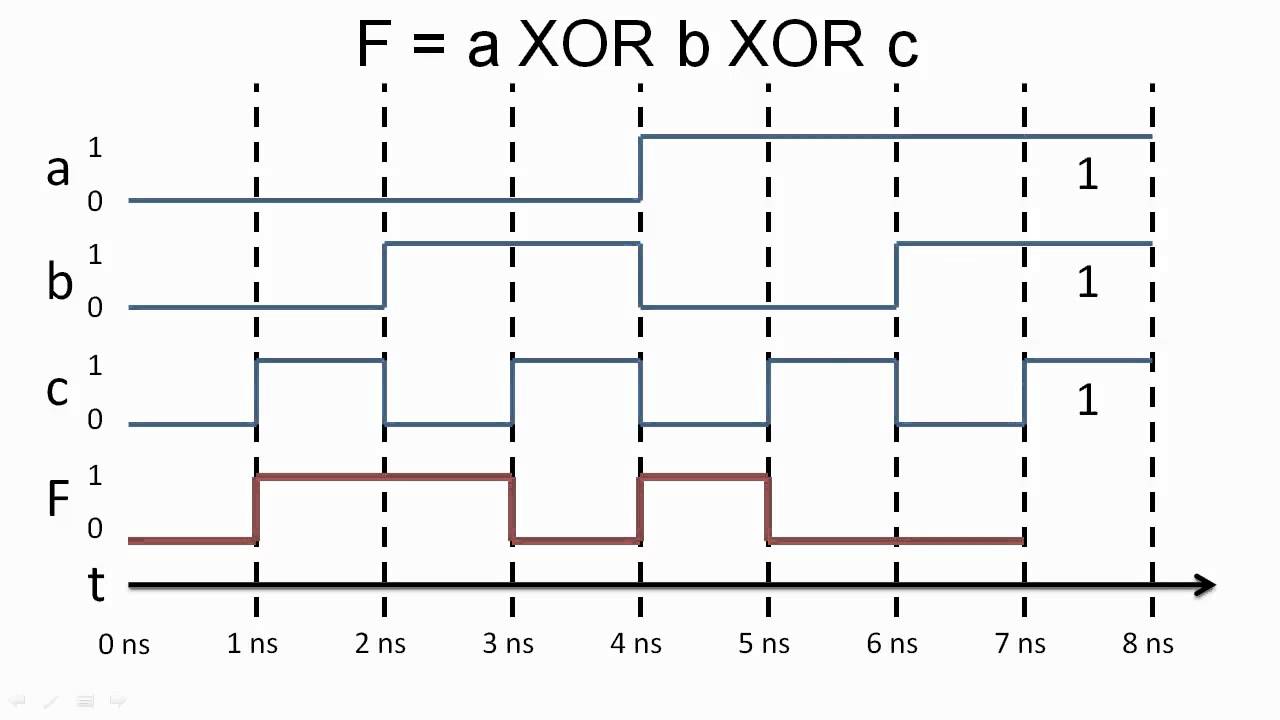

Feb 14, 2021 · Here, we have a diagonal pair in K-map. Therefore, it will relate to the XOR sign. And the expiration of D in terms of T is as the below equation. So, the circuit diagram of T flip flop using D flip flop need XOR gate connected as the below circuit diagram. Fig Circuit diagram of T flip flop using D flip flop. T Flip Flop Timing Diagram

Timing diagram. From the timing diagram it is clear that the output Q changes only at the positive edge.At each positive edge the output Q becomes equal to the input D at that instant and this value of Q is held untill the next positive edge . Characteristics and applications of D latch and D Flip Flop : 1.

Sep 27, 2017 · Thus, D flip-flop is a controlled Bi-stable latch where the clock signal is the control signal. Again, this gets divided into positive edge triggered D flip flop and negative edge triggered D flip-flop. Thus, the output has two stable states based on the inputs which have been discussed below. Truth table of …

D latch. Latches are designed to be transparent. That is, input signal changes cause immediate changes in output. With advertising revenues falling despite increasing numbers of visitors, we need your help to maintain and improve this site, which takes time, money and hard work.

If you’re just arriving, you should start from the beginning. Not just from the beginning of my story––I mean the *beginning*\-beginning. [My boyfriend Gavin’s story](https://www.reddit.com/r/nosleep/comments/lt331s/i_used_to_deliver_pizzas_now_im_a_driver_for_the/) will make mine a lot more clear. **\*\*\*** The bleating of the ambulance siren; cars swerving out of the way to the highway’s shoulder; Rhonda with her hand on Robbie’s, staring wide-eyed at the rose of blood blooming through the...

*At the world’s top college of magic and technology, every day brings a new discovery -and a new disaster. The advanced experiments of the college students tend to be both ambitious and apocalyptic, with the end of the world only prevented by a mysterious time loop, and a small handful of students who retain their memories.* *Freshman Vell Harlan, the newest student to get caught in the loop, now has to deal with stopping the apocalypse on a daily basis on top of having to study for exams- bu...

I posted a few weeks ago. Anyway, my problem has gotten worse. It was suggested I jam my trunk latch. Unfortunately, I cannot. It is too bent. I also don't know enough about cars or own any equipment to figure out if there is a short or not. My battery has been dying since January. It was rear-ended in December. Jumping it always worked. The car was stored from the end of January until July. I got a new battery and the problem began again a month later. The trunk light on the dash stays on at...

D . S . Logic Diagram . Schematic Symbol ... FIGURE 5-7. NAND "0" Latch. 5.2.2 Clock Signals . This circuit . is . known as a D· latch and the circuit input is " ... The solution to these problems is to provide a timing or clock signal that allows all of the flip-flops of the chained circuits

Hello, everyone! About two week ago I wrote a reply on one of the "which machine should I buy" posts about all the reasons I was excited about buying my new Brother PQ1500SL machine - even though it hadn't arrived yet. Someone requested that I give a review of it after I played with it a bit. This'll probably be long. **The Basics** The Brother PQ1500SL is a straight stitch only sewing machine with 8.6" of throat space, needle position, automatic cutter, needle threader, four feed dog position...

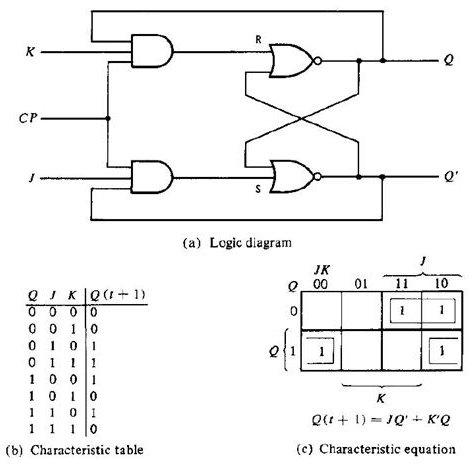

SR Latch with Control Input. S_ 1/S' 0/1. The complement output of the previous R'S' latch. Master-slave D flip-flop (1/2). „ Two D latches and one inverter „ The circuit samples D input and changes its output Q. Design description or timing diagram. Develop state diagram. Derive excitation equation.

The timing diagram is the diagram which provides information about the various conditions of signals such as high/low, when a machine cycle is being Address latch enable is an active high signal. (i.e.) the latch becomes enabled when the signal is high. It is activated during the beginning of T1 state of...

Disclaimer I do not own any of this, this is only a fanfic all credit belongs to bluefishcakes I originally wrote this for shits and giggles and i deleted my first post as a result of some people where saying some very nasty stuff to me about my writing and with the support of the many people such as with **Shadowflame** from discord who edited it and Grand-sea-emperor who kept pushing me to be a creative. Also following some of the advice of the truly lovely and supportive people on here in pa...

#Overview: As a first-time cultivator, I've noticed that a lot of the information regarding the well-known teks on /r/shrooms and Shroomery is spread throughout multiple different threads and found that it takes quite a bit of effort of going back and forth to properly understand some aspects of growing psilocybe cubensis. I have made this tek for the purposes of combining aspects of the Broke Boi Bulk Tek by /u/unemployedemt and aspects of Bod's Simplified Cultivation Methods, which span a coup...

Timing Diagram for the Gated SR Latch. Circuit Diagram for the Gated D Latch. This is the only new thing here. [ Figure 5.7a from the textbook ].

TLDR: Basically, my SNES will not output a clock signal to the controllers. All the controller circuits test OK from the connector to the CPU. Latch signal is OK. Video and sound are OK. Is there some other circuit that the CPU uses to generate the controller clock signal, or is my CPU bad due to the fact that it is able to generate a latch signal? I have a 1990 SNES with board SHVC-CPU-01 that will not generate a clock signal to either of the controllers. I have verified the latch and data sig...

A latch is a digital logic circuit that can sample a 1-bit digital value and hold it depending upon the state of an enable signal. Based upon the state of enable, latches are categorized into positive level-sensitive and negative level-sensitive latches.

OK, this "door-open-car-still-on" dinger has to fucking go one way or the other. I've scoured the internet from top to bottom looking for a solution to this that doesn't involve having to stick a screwdriver into my door latch every time I open it to trick the car into thinking the door is shut. I got ahold of a bootleg service manual and am looking at a diagram of a wiring harness with 4 wires going to the A23D Door latch assembly- driver side. The White/Yellow wire is described as being the ...

Timing diagrams. □ T flip-flops and SR latches. 2. CSE, Lecture The D latch. ◇ Output depends on clock. The Gated D Latch Timing Diagram. February 6, ECE A - Digital Design Principles 28 The Edge Triggered D Flip-Flop The D Flip-Flop (cont) State Diagram 1 0 D = 0 D = 1 D = 1 D = 0...

0 Response to "35 d latch timing diagram"

Post a Comment